昔ながらのIBM PC、PC/AT互換機からDOS/Vマシン、さらにはArmベースのWindows PC、M1 Mac、そしてラズパイまでがPCと呼ばれている昨今。その源流からたどっていく連載。第17回はいよいよ現在のスタンダード、PCI Expressが登場します。

2021年7月にISAからPCIへの変遷をご紹介したが、今回はその続編、PCIからPCI Expressへの移行をまとめたい。ちなみにこの筆者、放っておくと延々とバスの話を始めるのは“仕様”なのでご容赦いただきたい。

PCIは1995年辺りから普及し始め、1997年には既に主要なI/OのI/F(インタフェース)になった。とはいえ、いきなり既存のI/Fを転換するには時間が掛かる。ISAバスをPCのマザーボードでほとんど見なくなったのは、多分2005年とか2006年である。

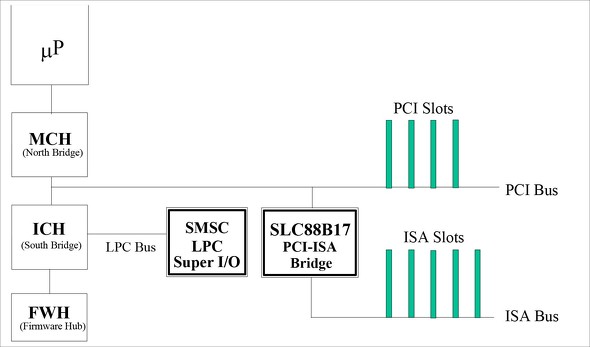

Intelは1999年に、Intel 810チップセットと併せて発表された初代ICHでISA Busのサポートを削除。PCIとLPC(Low Pin Count)という独自の低速周辺回路用I/Fを導入する代わりにISA Busを省いた。ただこの時点では、周辺チップメーカーがPCI-ISA Bridgeを提供しており、マザーボードメーカーはこれをオンボードで搭載してISA Busを出していた(写真1)。

写真1:SMC(Standard Microsystems Corporation:後に略称をSMSCに変更)のSLC88B17というPCI-ISA Bridgeチップの仕様書より。ちなみにSMSCは2012年にMicrochipに買収されている

写真1:SMC(Standard Microsystems Corporation:後に略称をSMSCに変更)のSLC88B17というPCI-ISA Bridgeチップの仕様書より。ちなみにSMSCは2012年にMicrochipに買収されているISA Busが消えたのは、次のPCI Expressの登場で低速周辺機器がPCIにほぼ移行し、ISAの必要性がなくなったからである。とはいってもまだこの時点では産業機器向けにはISAが結構必要とされており、確か2005年か2006年のCOMPUTEXでは、産業機器や計測器向けにISAを10スロットくらい持ったマザーボードが出展されていた記憶があるが、まぁこれは特定用途向けなので一般ユーザーには関係ない話である。

さてそのPCIであるが、1.0が1992年6月、2.0が1993年4月、2.1が1995年6月で、その後エラッタの修正が主な2.2が1998年12月、5Vキーを省いた2.3が2002年3月、5Vのサポートそのものが省かれた3.0が2006年7月にリリースされるが、ここで終わりとなっている。

その理由として大きいものは、PCI Expressが出てきたからという話であるが、その背景にはPCIのスケーラビリティーが限定的だったというのがある。PCIはバス幅32bit/信号速度33MHzのシェアードパラレルバスがスタンダードというか基本であるが、オプションでバス幅64bitが用意されており、またPCI 2.1では信号速度66MHzがやはりオプションで追加された。結果、

| バス幅 | 信号速度 | 帯域 |

|---|---|---|

| 32bit | 33MHz | 132MB/sec |

| 64bit | 33MHz | 266MB/sec |

| 32bit | 66MHz | 266MB/sec |

| 64bit | 66MHz | 533MB/sec |

の4種類の組み合わせが可能である。

後追いで、特にサーバ向けなどにより高い帯域を目指したPCI-Xと呼ばれる規格も追加され、こちらは、

| 64bit | 100MHz | 800MB/sec | |

|---|---|---|---|

| 64bit | 133MHz | 1067MB/sec | |

まで性能が引き上げられている。

64bit/133MHzではもう基本の8倍まで性能が引き上げられており、「スケーラビリティーあるじゃないか」と言われそうだが、PCI-Xはある意味拡張性を犠牲にした規格で、64bit/100MHzだとPCI-Xスロットが2本、64bit/133MHzだと1本になる。

実をいうと、さらに上を目指して64bit/266MHz及び64bit/533MHzの規格もPCI-X 2.0では追加されているのだが、こちらは一応1スロットで利用できるものの実装が極めて困難とされ、266MHzはIBMのサーバで実装例があるものの、533MHzは筆者が知る限り商用製品で採用した事例は皆無である。要するにある程度のスロットの本数をサポートしようとすると、信号速度は66MHzに限られる。

また、32bitの信号線の引き回しだけでもかなり難しい(しかも信号長が変わると、信号のバラつきが大きくなるので、「なるべく」等長配線が望ましいとされる)のに、64bit化するとさらに配線が困難になる。結局のところ、32bit/33MHzのシステムが大多数で、サーバ向けに多少64bit/33MHzとか32bit/66MHzのPCIが用意された、という程度でしかなく、これは1990年代では十分な速度であったが、2000年代に入るとまたもやPCIの速度がボトルネックになり始めていった。

PCIの速度がボトルネックに

最初に問題になると予想されていたのはグラフィックスであった。ちょうどこの頃からグラフィックス表現に3Dが加わり始めたことで、「PCIのままではTexture Data(テクスチャデータ)の転送が間に合わない」と考えられた。Texture Dataとは3Dのポリゴンの表面に張り付ける「模様」であるが、3D描画を高精細にすると必然的にこのTexture Dataの量が多くなり、グラフィックスカードのVRAMに乗りきらなくなるので、メインメモリにTexture Dataを置いて随時転送する形にしないと間に合わないと予想された。

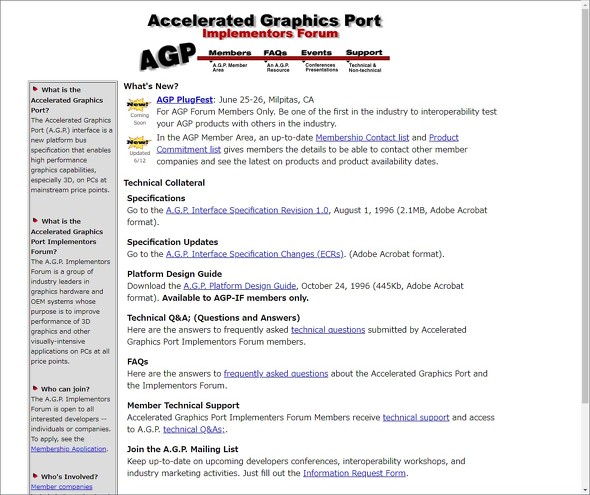

そこで、グラフィックスカード専用にPCIを改造(魔改造?)した規格としてIntelが提唱したのがAGP(Accelerated Graphics Port)である。PCI-SIGではなくIntelが提唱した辺りが魔改造らしさを助長しているが、同社はこれを独自規格とするのではなく、AGP Implementation Forumを立ち上げ、ここにSpecificationを寄贈しており、それもあって「一時的に」PCにおける事実上の標準規格になった。

AGP 1.0は1996年7月にリリースされるが、これはPCIの32bit/66MHzをベースに、8bit幅のSide Bandと呼ばれるアドレス伝達用のバスを追加して、アドレス転送をここでやるようにして転送効率を上げたり、GART(Graphics Address Re-mapping Table)と呼ばれる仕組みを取り入れてテクスチャを置いたメインメモリを直接グラフィックスカードからアクセスできるようにするといった、もうグラフィックスカード専用に拡張したものである。転送モードは1x(32bit/66MHz)と2x(32bit/66MHz DDR)の2つで、2xだと533MB/secの転送速度が実現できた。

これはまぁチップセットのすぐそばにAGPスロットが1本だけあったから、ここまで信号速度を上げても何とかなったというべきか。

このAGP 1.0は信号電圧が3.3Vだったが、1998年3月には電圧を1.5Vに落とすとともに4x(32bit/133MHz DDR)モードが追加されたAGP 2.0が登場し、転送速度は1067MB/secに。2002年8月には電源電圧を0.8Vに下げ、8x(32bit/266MHz DDR)モードが追加されたAGP 3.0がリリースされ、転送速度は2133MB/secまで引き上げられた。

さらに、消費電力が増える一方のビデオカードに対応するため、電力供給ピンを追加したAGP Pro仕様も後追いの形で追加されている。

ただ、ではAGPの意味があったか? と言われると、実はほとんどなかった。AGP 1.0の頃と言えば、例えば1997年に登場したNVIDIAのRIVA 128は、オンボードで128bit/100MHzのSGRAMを搭載、メモリ帯域は1600MB/secであり、AGP 2xの3倍高速で、メモリ容量も4MBだったから、メインメモリの1/4程度は確保されていた。AGP 3.0の頃だとATIのRADEON 9700 Pro(2002年9月発表)が256bit/325MHz DDR-SDRAMだから帯域は20GB/secほど。メモリ容量も128MBあった。

要するにAGPの速度は、いつの時代においてもビデオカードのオンボードメモリの数分の1の帯域しかなく、またメモリ容量もわざわざメインメモリを使う必要がない程度に充実していた訳だ。

こうなると、テクスチャをAGP経由で取り込む動作は深刻にゲームの進行の妨げになる(実際猛烈にフレームレートが落ちる)ため、ゲームデベロッパーは何とかしてオンボードのメモリ内に必要なテクスチャを押し込む(か、ゲームシーンの切り替え時期に必要なテクスチャのロードを行うことにして、ゲーム中はロードをしない)よう工夫することになり、結局AGPのメリットはほとんど生かされなかったとして良い。それもあって、次のPCI Expressが出ると、急速にAGPは衰退していくことになった。

余談になるが、AGP Implementation Forumのサイトは2006年頃までは存在していたが、その後ドメインが売られたようで、なぜかロシア語のAGPのサイトになったり、妊娠と性病のサイトになったり、フランス語の謎の情報サイトになったりと変遷を続けており、直近ではドメインの登録がなくなっている。

第3世代I/O、PCI Expressの登場

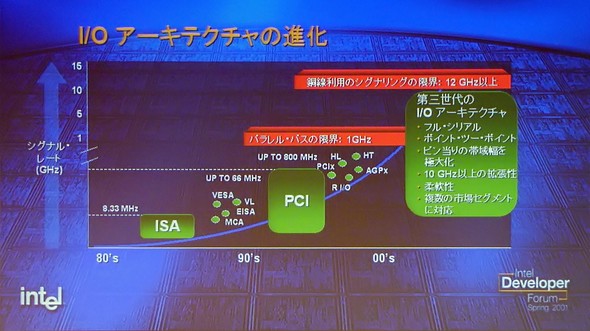

次はそのPCI Express。もともと2001年の春ごろ、「現在次世代向け規格の作業を行っている」という話がIntelから出ていた(写真3)。

写真3:これを説明したのは誰あろう現在のIntel CEOであるパット・ゲルシンガ−氏。当時の肩書きはCVP兼CTOだった。これは2001年4月に行われた、IDF 2001 Spring Japanにおける講演から

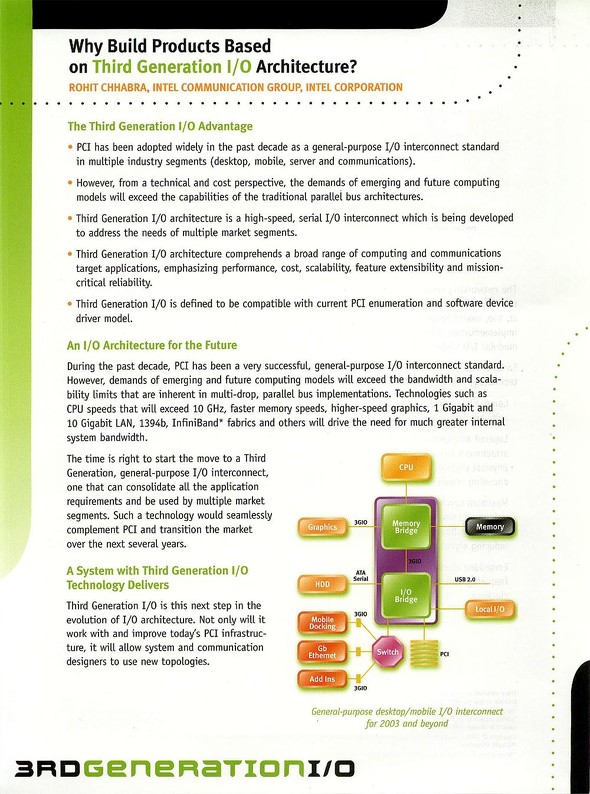

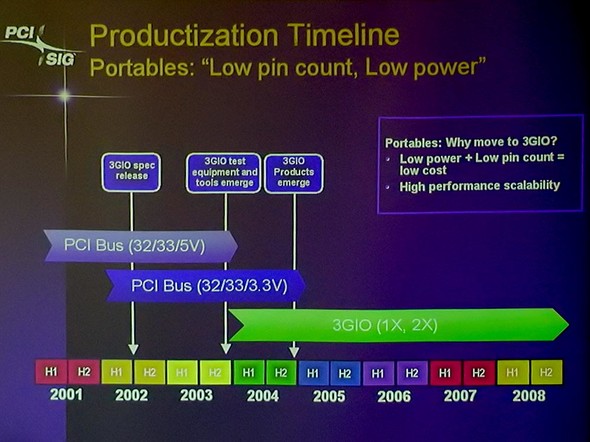

写真3:これを説明したのは誰あろう現在のIntel CEOであるパット・ゲルシンガ−氏。当時の肩書きはCVP兼CTOだった。これは2001年4月に行われた、IDF 2001 Spring Japanにおける講演から同年秋のIDFでは“3GIO”(3rd Generation I/O)という名称で概略の説明があり、またPCI-SIGからも2005年辺りから製品が投入されるという見通しが語られた(写真5)。

3GIOそのものの骨子はIntelが開発した(開発を率いていたのは、ここでも出てきたアジャイ・バット氏である)が、早い時期からPCI-SIGと共同での作業となっており、仕様はやはりPCI-SIGに寄贈され、Revision 0.7辺りからほぼPCI-SIG側で仕様策定のハンドリングが行われている。

実際にPCI ExpressのBase Specification 1.0は2002月7月にリリース、さまざまなベンダーがこれに取り組んでいく。

とはいえ、当初はPCI Expressの実装がかなり大変だったのは事実である。例えば当時VIA Technologies傘下だったS3はDelta Chrome GPUの開発をしていたが、PCI Expressを統合するとダイサイズが倍になるとかいう話で、次世代(Chrome S)までPCI Expressの統合を先送りにしている。

NVIDIAはGeForce 6000シリーズで初のPCI Express対応を果たすが、そのGeForce 6000シリーズはHSI(High-Speed Interconnect)という名称のAGP/PCI Express Bridgeチップ経由での対応になっていた。

ATIはこれに対して「当社はNativeでPCI Express対応だ」とアピールしたが、そのATIも同時期に投入されたX800こそNative PCI Express対応だったものの、下位にあたるX600シリーズはやはりAGP/PCI Express Bridgeを利用していることが後でバレるといった具合に、各社苦労していた。

技術的に見れば、PCI Expressでは、

- パラレルバスを廃し、Point-to-Pointのシリアルバス形式。また信号にDifferential(差動式)を使う事で信号の高速化とノイズ耐性強化を狙う。ちなみに送受信は別の信号線を使うので、結局1レーンあたり4本の信号線が必要。

- 送受信のタイミング制御のためのクロック信号を、データ信号に埋め込むEmbedded Clockを採用。クロック信号+8bit分のデータを10bitのシンボルにして、このシンボルを2.5GHzの速度で転送する(ので、表記は2.5GT/secとされる事が多い。2.5G Transfer per secの略である)。このため1レーン当たり250MB/secの双方向となる。

- 1対のレーン(x1)以外に、2/4/8/16/32対(のちにx12なども追加されたが、最新版ではx32と併せて削除された)の信号を束ねて送るという技法が採用された。これがパラレルバスと異なるのは、電気的には各々は別の信号として扱われ、上位プロトコル層(正確にはDataLink層)で束ねた形になる点である。これにより配線はあくまでも1対2本単位で等長でありさえすればよく、配線がだいぶ楽になっている。また必要とする帯域に応じてレーン数を調整しやすいのもメリットとされる。

- アプリケーション(つまりOSとかデバイスドライバ)から見ると、PCIとの互換性が保たれている(多少拡張はしているので、その追加分のハンドリングは必要だが、そうしたものはデバイスドライバで吸収されているので、OSからはPCIとPCI Expressが等価に見える)

といった点が特徴になる。

当初は2.5GHzという高速信号を通すために苦労したようだが、幸いにもRambusのDirect RDRAMである程度技術の底上げがなされていたこともあり、Direct RDRAMのときほどには問題にならなかった。

チップセットとしてもIntel 915とかATIのRadeon Xpress 200、NVIDIAのnForce 4、VIAのPT880 Ultra/PM880/K8T890など2004年以降に登場したものは各社グラフィックス用のI/FがAGPからPCI Express x16に切り替わり、ただしグラフィックス以外はまだPCIという状況が続いた。

それでも2010年手前には、例えばストレージカード(RAIDコントローラー)とかEthernet、Soundカード、USB拡張カードなどが相次いでPCI Expressに移行を果たし、その一方でPCIのスロットはどんどんマザーボードから減っていくようになった。PCI Express自体もどんどん進化しており、2007年には速度を5GT/secに引き上げた2.0、2010年には8GT/secに引き上げた3.0、2017年には16GT/secの4.0、2019年に32GT/secの5.0と来て、2022年にはついに64GT/secの6.0がリリースされている。

実効転送速度ではx1レーンで1.0が250MB/sec、以下2.0が500MB/sec、3.0が1GB/sec、4.0が2GB/sec、5.0で4GB/sec、6.0では8GB/secまで引き上げられている。

高速化を牽引したのはグラフィックスではない

ただ面白いのは、これまでPCI→AGP→PCI Expressという変遷の牽引役だったグラフィックスカードは、PCI Express 3.0辺りでほぼその役割を終えている。理由は簡単で、AGPの効果がなかったのと同じく、外部バスをいくら高速にしても性能にほとんど差がないためである。

実際、例えばPCI Express 3.0 x16対応のビデオカードをPCI Express 2.0 x16で使ったり、あるいはPCI Express 3.0 x8相当で使ったりしても、性能は数%変わるかどうかという程度でしかない。正直に言えばこれはAGPの時代から全く変わっていないのだが、マーケティング的な理由でこれをはっきり言えなかった、というのが正確なところか。

そのグラフィックスカードに代わって、新たなPCI Expressの牽引役になったのはストレージとネットワーク、アクセラレータである。特にストレージは、2009年にSATAやSASといったストレージのプロトコルをPCI Express上に通すNVMe(Non Volatile Memory Express)という規格が決まり、当初はサーバ向けがメインだったはずなのが、コンシューマー向けにもNVMe M.2 SSDというPCI Express x4レーン向けの規格が普及し始めたことで爆発的にそのニーズが増えた(この辺の話はまたいずれ)。

同様にネットワークやアクセラレータなどは、グラフィックスよりももっと切実に「より広い帯域」を必要としており、こうしたものがPCI Express 4.0以降は明確な牽引役の主役に躍り出た感じだ。

既にPCI Expressは単にPCだけでなく、サーバや産業機器、小さな組み込み機器でも使われるようになっており、USBと並んで広く使われる規格になっており、さらにさまざまな規格がPCI Expressを利用して構築されるようになっている。もう昨今では組み込み機器でもPCIを使うケースはほぼレアになっており、USBかPCI Expressかといった感じになっている。

Intelは2010年に投入したIntel 5シリーズチップセットまではPCIのサポートを継続していたが、次のIntel 6シリーズではサポートを打ち切っている。ただISAのときと同じく、しばらくはPCI Express/PCI Bridgeを介する格好でPCIスロットがマザーボードに残り続けた。

これもなくなり始めたのは、2013年のHaswell世代(Intel 8シリーズチップセット)が市場に登場した辺りだろうか? PCI Expressが登場してからも10年近く、PCIはPCの主要な拡張バスであり続け、その後でようやくPCI Expressにその座を譲った格好だ。

関連記事

からの記事と詳細

https://ift.tt/ucl760Z

科学&テクノロジー

Bagikan Berita Ini

0 Response to "もうPCIでは遅すぎる さらなる高速化目指すPCはPCI Expressへ - ITmedia NEWS"

Post a Comment